U.S. chip tariffs and what they mean now

Tariffs, exemptions, and new photonics capacity are rapidly re-shaping the chip map.

The U.S. is signaling tougher semiconductor trade rules, potentially using tariffs and “1:1” domestic-production targets. Meanwhile, Europe just boosted a 300mm silicon-photonics program geared to aid development in AI, data centers, and telecom.

Together, these moves could reroute demand, pricing, and lead times across component categories from logic and memory to optical interconnects.

U.S. tariffs aim to shift Southeast Asian chip production

The Trump administration has repeatedly threatened new semiconductor tariffs for companies that aren’t willing to fall in line with its vision of a market with the U.S. back on top as a key chip player. A surprising signal from Washington now gives those threats a new face, tying them to a “1:1 rule” that links chip import volumes to equivalent domestic production.

If implemented, this model would be a significant shift from reactive trade barriers in favor of a heavy-handed approach to incentivizing reshoring. According to recent reports from Reuters and The Wall Street Journal, the 1:1 mechanism being considered would allow U.S. importers to bring in chips tariff-free—so long as their operations generate an equivalent volume of chips domestically over time. Companies failing to meet this benchmark could face escalating tariffs. Lawmakers are also reportedly discussing grace periods or production credits that would help companies account for long lead times or new fab buildouts.

Notably, this proposed policy hasn’t been officially introduced, and lawmakers have warned that reports about it should be considered speculative at this time. That said, the implications would be massive as chip tariffs would effectively become a dynamic compliance tool used to influence both capital investment and supply chain operations of companies doing business in the U.S. and internationally.

Although the policy hasn’t yet been adopted, the U.S. trade envoy in Kuala Lumpur issued a strong signal of intent by recently telling Southeast Asian chipmakers that they must consider “shifting production to the United States or face a tariff solution.”

That warning comes against the backdrop of existing 10-40% tariffs on many Southeast Asian exports. Experts from the region fear that number will rise significantly if semiconductors are pulled further into the crossfire.

Given the multi-country packaging and testing workflows that commonly run through Malaysia, Taiwan, and Vietnam, the practicality of implementing fresh chip tariffs is uncertain. This is especially true for U.S. companies selling end products with embedded or multi-sourced chipsets imported from international fabs. Establishing traceability standards granular enough to assign liability in such cases and hold up against a 1:1 tariff structure would require unprecedented coordination across supply chains and allied nations.

Until the administration releases the findings of its national security trade investigation into chip imports, it’s difficult to speculate what the tariff situation will truly look like in the coming quarters. For now, uncertainty continues to reign. The Trump administration’s repeated semiconductor tariff threats, as well as promises of carve-outs for companies investing in U.S. fabs, have come with little to no actual guidance, sowing confusion among supply chain planners and chip execs alike.

If the 1:1 proposal follows a similar path, it will only deepen the complexity of long-range planning and further blur the line between trade enforcement and industrial policy. Though some firms like TSMC, Micron, and GlobalFoundries, which have plans to increase U.S. production, may benefit, the fallout is less clear for the rest of the industry.

For companies navigating this volatile environment, flexibility is essential. Sourceability’s engineering team can help identify verified form-fit-function alternatives and drop-in options to reduce your organization’s exposure to tariffs tied to opaque rules or shifting country-of-origin designations.

Europe’s 300mm silicon-photonics push

While the U.S. focuses on tariffs to reshape semiconductor manufacturing, Europe is reinforcing its joint collaborative approach. STMicroelectronics’ recent announcement of the STARLight initiative marks a critical milestone in the continent’s bid to localize high-value photonics manufacturing in the immediate future. The move quietly lays the groundwork for independence in chip infrastructure critical to AI, telecom, and automotive applications.

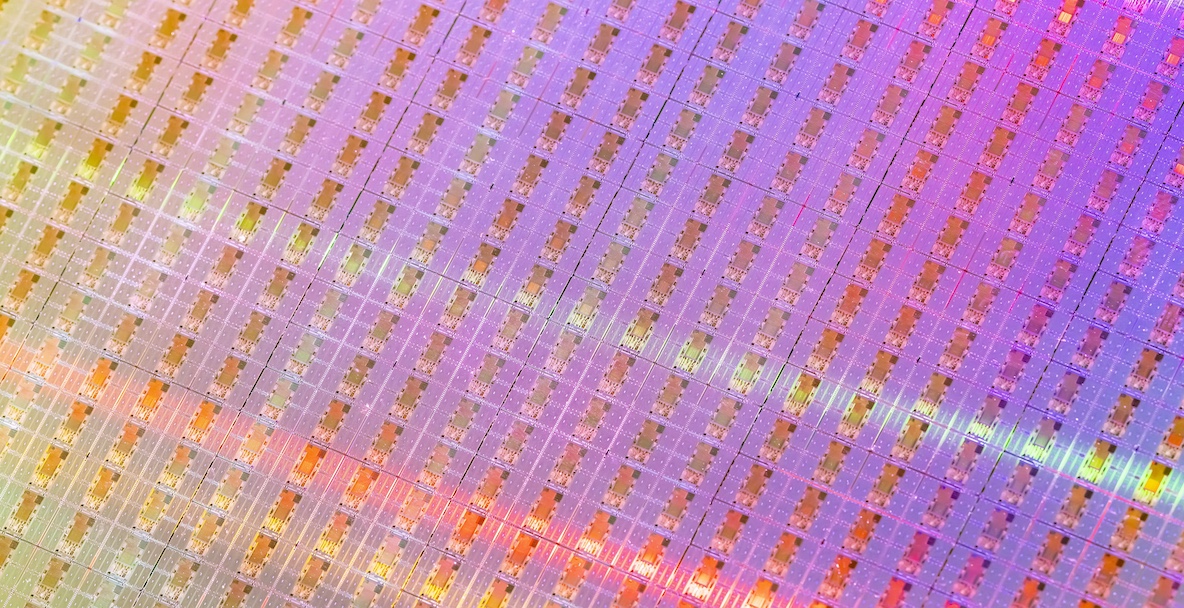

Funded through the EU Chips Joint Undertaking, STARLight brings together 24 companies and research institutions across 11 countries, forming the region’s most ambitious silicon-photonics (SiPho) consortium to date. The program’s core objective is to establish volume production of SiPho on 300mm wafers. This is a notable leap from the 200mm pilot lines still prevalent across much of Europe.

The STARLight roadmap prioritizes advancements in on-chip laser integration, advanced materials engineering, and high-efficiency packaging. Each of these has been a bottleneck that traditionally limits the scalability of photonics components manufacturing.

The timing of this project is particularly relevant given the boom in AI data centers and an increasing desire for faster performance. Physical limits of traditional copper interconnects for transmitting data at high frequencies in an AI data cluster context position optical modules as the go-to technology of the future. Europe’s move to prioritize development in this area is an indicator of the continent’s belief that AI will continue to be a market-defining force for years to come.

Of course, it also bears relevance from a strategic perspective. Anchoring high-value photonics manufacturing in the EU could serve as a counterweight to the tug of war between the U.S. and China over advanced semiconductors. STARLight will help reduce dependency on both North American and Asian supply chains at a time when tariffs and geopolitical upheaval are forcing many companies to rethink their sourcing strategies.

At the same time, the move will likely introduce some near-term supply volatility. As key STARLight members scale up R&D and pre-production runs, foundry capacity may tighten, and lead times could extend for optics components. Integration challenges between traditional CMOS and emerging photonics packaging platforms may also spur short-term delays as new substrates and tools come online.

Looking ahead, procurement teams should monitor their BOMs for any optics items that could be impacted by these transitions. Market trend forecasting tools can help anticipate lead time volatility tied to regional developments like STARLight. Alternate sourcing strategies for critical optoelectronic components will also be crucial to resilience in the coming quarters.